### From Decadal Plan to actionable all-industry Roadmap

Victor Zhirnov

Chief Scientist

Victor.Zhirnov@src.org

Victor Zhirnov

Semiconductor Research Corporation

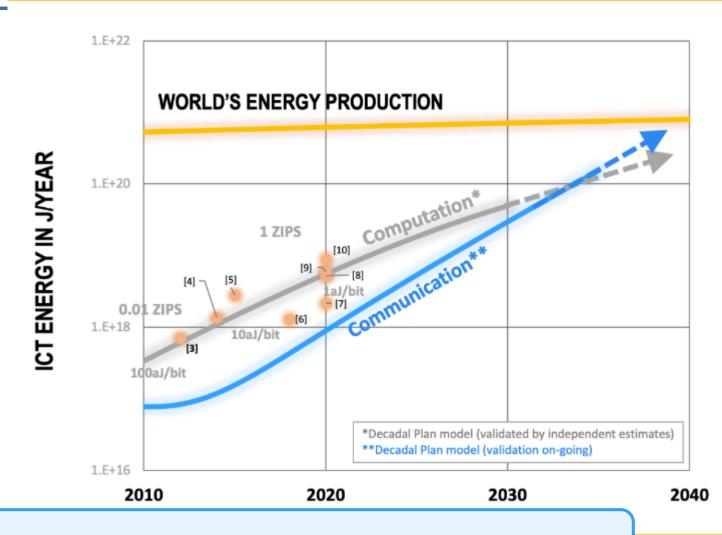

# ICT ENERGY COMPUTATION AND COMMUNICATION

By design, the Decadal Plan focuses on WHAT to accomplish, not HOW to accomplish it.

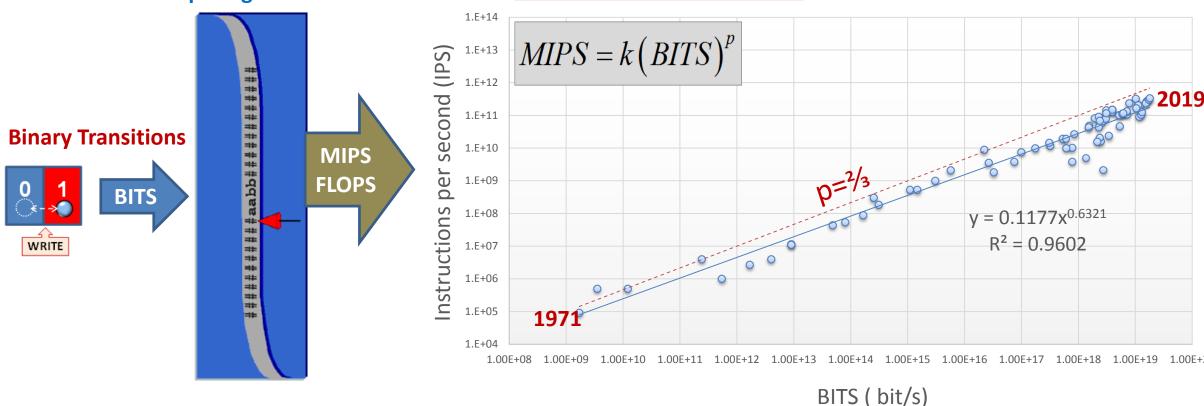

### **CPU** operations vs. binary transitions

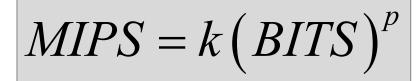

$k=0.1, p=0.64 \approx \frac{2}{3}$

The key question is bit-utilization efficiency in computation

$$\beta = \alpha N_{tr} \cdot f$$

$$P = \beta E_{bit}$$

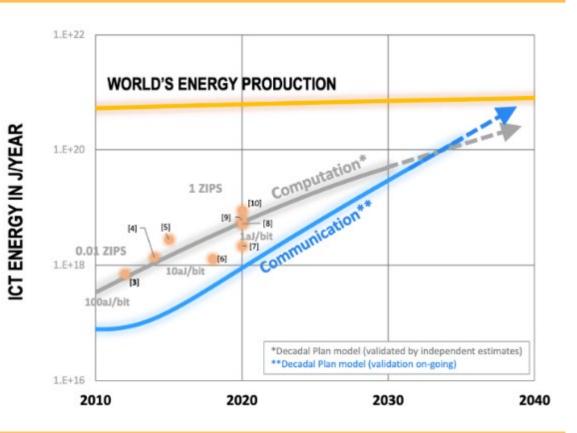

### Compute Energy Challenge

## ICT ENERGY COMPUTATION AND COMMUNICATION

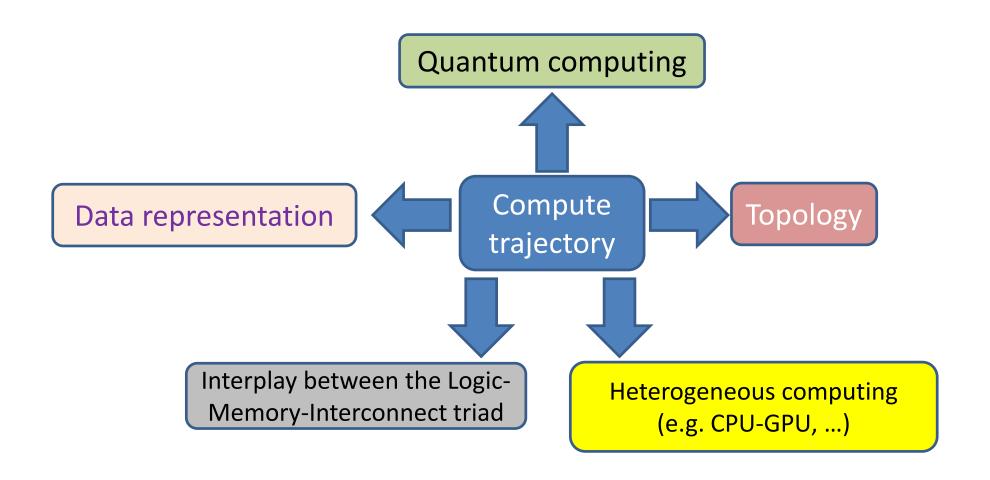

- Discover compute trajectories with  $p{\sim}1$

- How do we get from  $\sim 2/3$  to 0.9 or 1?

- What "silicon" solutions can push the coefficient toward 1?

- Does Al?

- Does Neuromorphic?

- Does Quantum?

### Research directions towards new compute trajectories

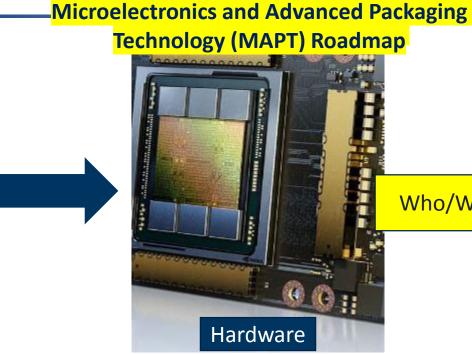

### MAPT: A natural next step for Decadal Plan

**Decadal Plan** defines **WHAT** is needed

Plan for 10 years

$$MIPS = k \left( BITS \right)^p$$

**MAPT Roadmap**

defines **HOW** to accomplish

MAPT team is developing the first industry-wide 3D semiconductor roadmap to guide the forthcoming microelectronic revolution

Who/When/Where? Support

**CHIPS Funding**

implementation plan

- Industry, academia, gov. labs

- NSTC, NAPMP

- SRC Manufacturing Inst.

The MAPT roadmap needs to be aligned with the DOE Energy-efficiency roadmap

#### **Thank You**

Victor Zhirnov, Chief Scientist: victor.zhirnov@src.org

David Henshall, Director of Business Development and Government Relations: <a href="mailto:david.henshall@src.org">david.henshall@src.org</a>

Todd Younkin, President and CEO: todd.younkin@src.org