## U.S. DEPARTMENT OF

Office of ENERGY EFFICIENCY & RENEWABLE ENERGY

ADVANCED MATERIALS & MANUFACTURING TECHNOLOGIES OFFICE

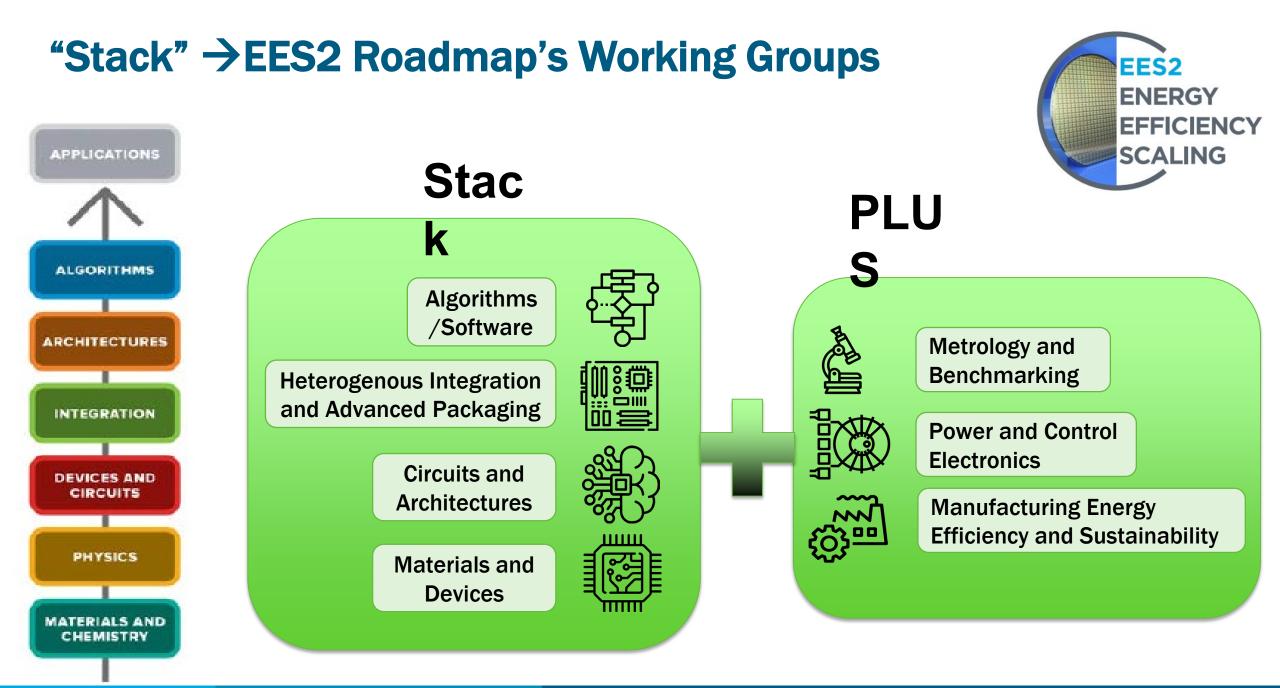

## Welcome to EES2 and FINAL Roadmap Working Group Meeting #9

Tina Kaarsberg, PhD EES2 Workshop Co-Chair

August 16, 2023

https://microelectronics.slac.stanford.edu/amo-microelectronics

## **Climate Change: Code RED for Humanity**

Last month was the hottest month ever recorded for the planet, this month showed more extreme weather impacts

## Maui Wildfires

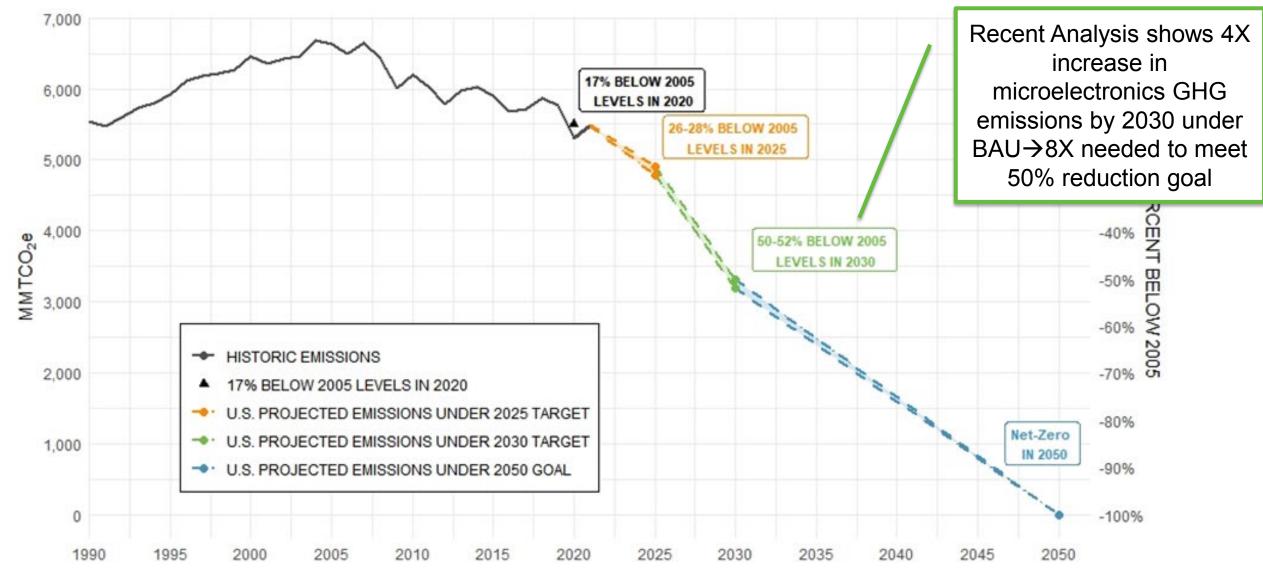

## **US International Agreements on GHG Reductions**

From White hous ergov elege 2021 CReportvalle energy advanced materials and manufacturing technologies office

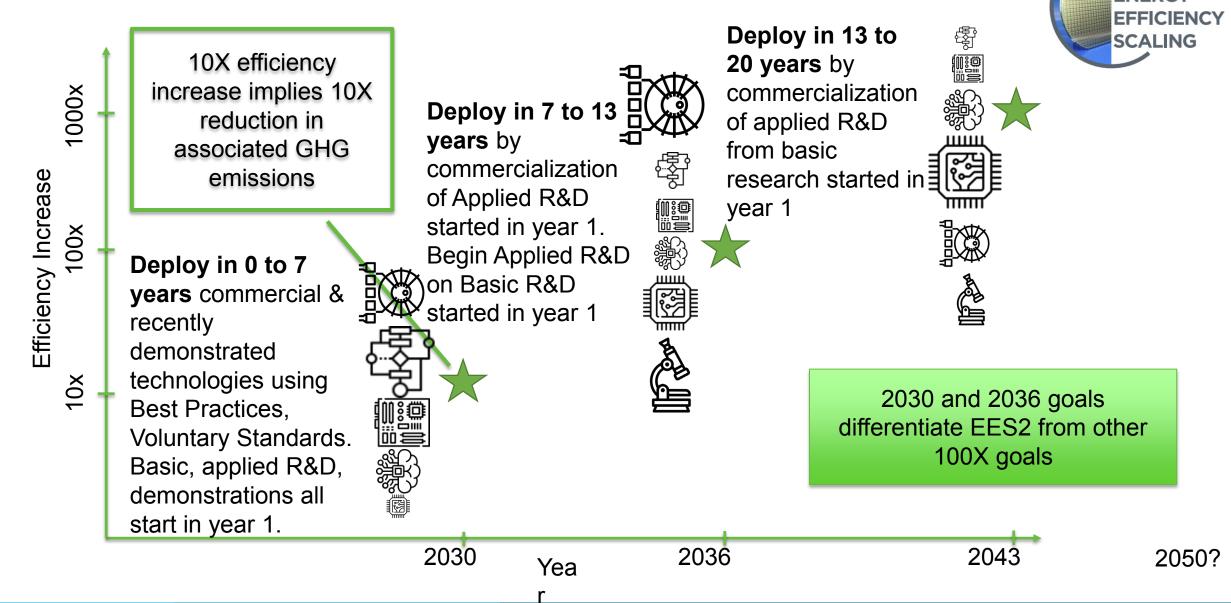

## Under EES2, Microelectronics is doing its part by 2030

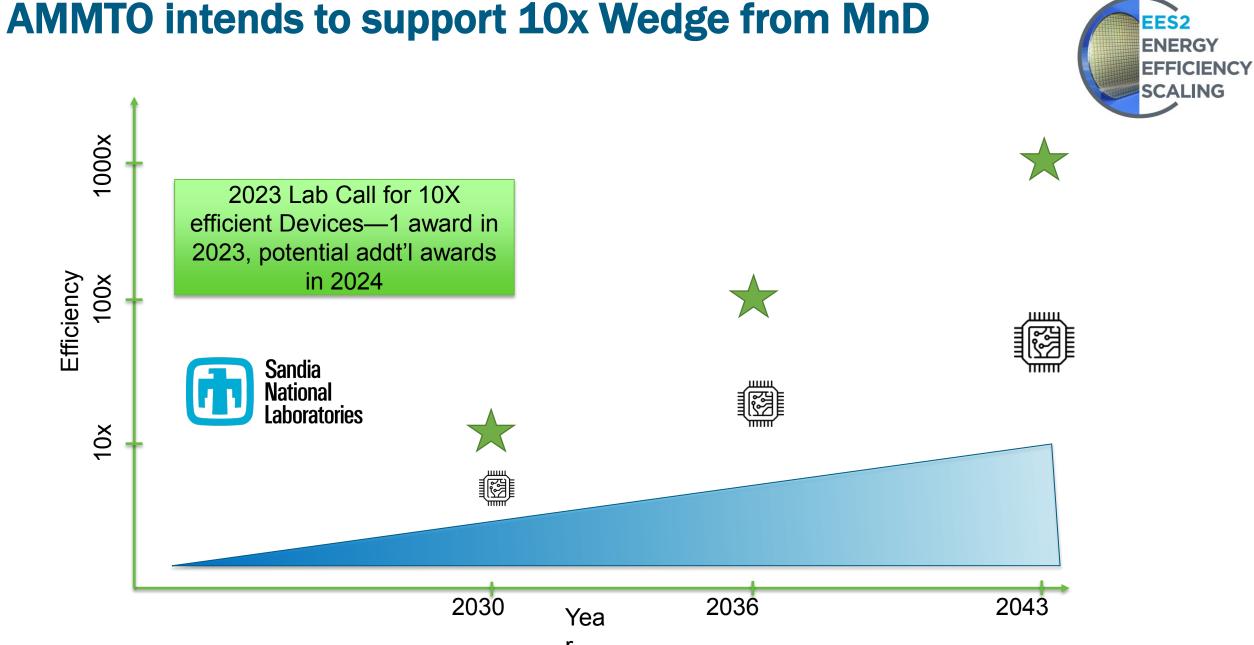

## Today's Announcement: 1st EES2 R&D Award a 10X Energy Efficient vTFET to replace MOSFET

#### **Technology Summary**

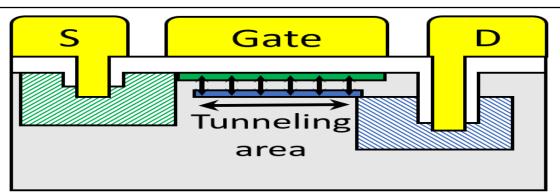

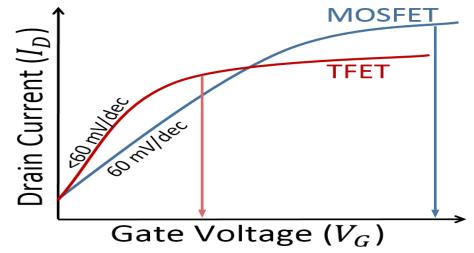

Project will experimentally and theoretical verify energy efficiency and speed of a silicon vertical tunnel field effect transistor (vTFET) made using atomic precision advanced manufacturing (APAM). The vTFET reduces the voltage compared to conventional microelectronic transistors by 3X (see figure at right), leading to 10X improvement in fJ/switch. Design leverages the atomically abrupt doping profiles and record-breaking dopant densities achieved by APAM, which also enables the vertical geometry that increases current.

#### **Deliverables**

36 months; Federal funding \$4M

| Year 1 | -Create experimental & modeling platforms                                                                                                     |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Year 2 | -Measure tunneling devices with combinations of gated layers, commercial epi, and APAM epi<br>-Create multi-scale model based on real devices |

| Year 3 | -Demo real vTFET and simulate energy eff.<br>-Contrast commercial and APAM epi for vTFET                                                      |

#### **Key Performance Metric**

3X reduced voltage  $\rightarrow$  10X reduced power consumed by entire processor

### **Technology Commercialization Strategy**

In addition to demonstrating the vTFET, Sandia will build a multi-scale modeling framework, based on real devices, that includes the quantum mechanics of tunneling and enables optimizations to include cost-lowering and performance enhancing features only available to industry. Combined with experimentation on the differences between APAM-based and conventional epitaxy-based devices, Sandia's project will provide industry with the motivation and tools to deploy the vTFET as a 10X energy efficient, general purpose, CMOS-compatible, drop-in alternative to MOSFET. To increase likelihood of industry uptake, Sandia is seeking members for an Industrial Advisory Board.

#### 10x energy efficiency in general purpose, Si-based transistors

## **And There's More!**

## WG Results Table to be included in NIST MAPT!

| Working Group                                       | Energy Efficiency Technology      | Near Term (0-5yrs)                                                                                                                                            | Mid Term (5-10 yrs)                                                                                                                                                                                              | Long Term (10+ yrs)                                                                                                                                                                              |

|-----------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Materials and Devices                               | Key Energy Efficient Technologies | CNTFET (logic)                                                                                                                                                | TFET                                                                                                                                                                                                             | Analog devices for neuromorphic                                                                                                                                                                  |

|                                                     | Key Challenges                    | <ul> <li>Production of pristine and near-pure<br/>population of CNTs.</li> <li>Reducing CNT contact resistance.</li> </ul>                                    | <ul> <li>Fabrication of consistent tunnel<br/>junction. Currently, variability is high.</li> <li>Demonstration of high on/off ratio<br/>and low voltage operation.</li> </ul>                                    | <ul> <li>Down-selecting from a wide breadth of<br/>materials, designs, and approaches that fit need.</li> <li>Performance loss during integration with<br/>conventional technologies.</li> </ul> |

|                                                     | Key Energy Efficient Technologies | Domain Specific Architectures                                                                                                                                 | EDA                                                                                                                                                                                                              | Compute in Memory                                                                                                                                                                                |

| Circuits and Architectures                          | Key Challenges                    | <ul> <li>Architecture is set up after software</li> <li>ASICs are not adaptable to other systems</li> </ul>                                                   | <ul> <li>Simulation of device function is<br/>limited</li> <li>3D stacked technologies are lacking</li> </ul>                                                                                                    | <ul> <li>Technology is available, however software<br/>difficulties are preventing integration</li> </ul>                                                                                        |

|                                                     | Key Energy Efficient Technologies | Advanced Thermal Interface Materials                                                                                                                          | CNT Global Interconects                                                                                                                                                                                          | Monolithic Integration                                                                                                                                                                           |

| Advanced Packaging and<br>Heterogeneous Integration | Key Challenges                    | <ul> <li>Thermal resistance at interfaces is<br/>poorly understood</li> <li>CTE material mismatch can cause<br/>cracking and lowering heat removal</li> </ul> | <ul> <li>Contact resistance between<br/>CNT/Metal is high and poorly<br/>understood</li> <li>Deposition methods for vertical CNT's<br/>require high temperatures which may<br/>not be BEOL compatible</li> </ul> | <ul> <li>Thermal management during operation</li> <li>Higher tiered technology has lower</li> <li>performance due to thermal budget constraints</li> </ul>                                       |

# Still More!Preliminary Version for WG ReviewWG Results Table to be included in NIST MAPT!

| Working Group                 | Energy Efficiency Technology      | Near Term (0-5yrs)                         | Mid Term (5-10 yrs)                                            |                                                                        | Long Term (10+ yrs)                                                                      |

|-------------------------------|-----------------------------------|--------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|                               | Key Energy Efficient Technologies | Resource-Aware Workload Scheduling         | Improved Tra                                                   | aining Algorithms                                                      | Optimization of memory access in algorithms                                              |

| Software and Algorithms       | Key Challenges                    | Near-real-time resource availability       | <ul> <li>Achieving c</li> <li>Data/dimenspecificity</li> </ul> | ontinual/sequential learning nsional reduction and                     | <ul> <li>Optimization depends on architecture</li> <li>Software compatibility</li> </ul> |

| Power and Control Electronics | Key Energy Efficient Technologies | End-to-end power delivery for data centers | Use of wide bandgap power devices and optimized technologies   |                                                                        | Power deliery for photonic integrated circuits                                           |

|                               | N                                 | Metrology Technology Approach              |                                                                |                                                                        | Challenges                                                                               |

|                               |                                   |                                            |                                                                | <ul> <li>Bridging the gap between i<br/>system performance.</li> </ul> | dealized system metrology and actual                                                     |

| All metrology                                                     | <ul> <li>Bridging the gap between idealized system metrology and actual system performance.</li> <li>Dearth of samples to develop new metrology techniques.</li> <li>Avoid excessive measurements, understanding process dependency to capture only what's necessary.</li> </ul> |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3D metrology (thermal, interface, etc.)                           | <ul> <li>Inability to evaluate properties of interest at inaccessible points within 3D structures without typically resorting to destructive techniques.</li> <li>Very large data sets from 3D metrology – hard to manage.</li> </ul>                                            |

| Material property measurements, including thin film and patterned | <ul> <li>Inaccuracy of material and interface properties that are used in<br/>computational models of 3D structures.</li> </ul>                                                                                                                                                  |

| materials                                                         | <ul> <li>Most material property measurements based on bulk materials,<br/>when using these materials in real systems, they are at micro/nano<br/>scales (i.e., thin films) where material properties are different.</li> </ul>                                                   |