#### DATE 05/24/2023

### ROLE OF HETEROGENEOUS INTEGRATION FOR ENERGY EFFICIENCY

MOINUDDIN AHMED, Ph.D. Technical Lead Electronic Materials Characterization Group Applied Materials Division

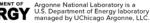

### FUTURE OF COMPUTING More Moore

#### **Challenges:**

- End of Dennard Scaling

- Scaling transistors down improves speed and reduces energy consumption

- Heat removal issues- clock-based scaling

- Focus: more power efficient and less expensive to build

### FUTURE OF COMPUTING More Moore

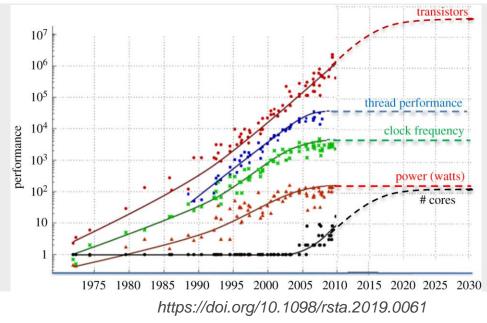

- End of lithographic scaling

- ITRS report predicts transistor scaling will end in 2021

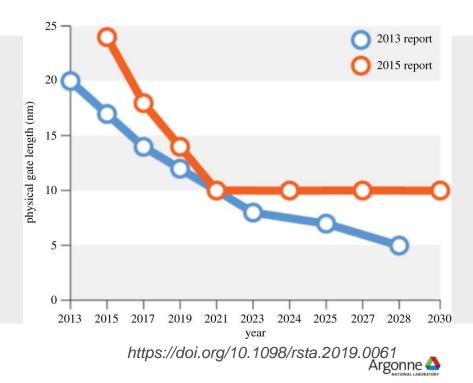

### FUTURE OF COMPUTING More than Moore

Integrating functionalities at system level

More functions lower system cost

Adding analog, RF, MEMS, HV circutir, control and passive components

### More than Moore and Beyond's Moore

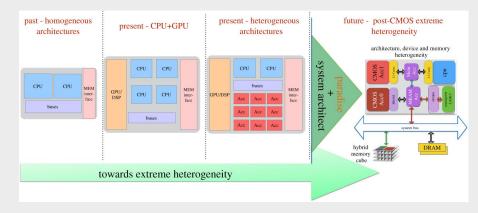

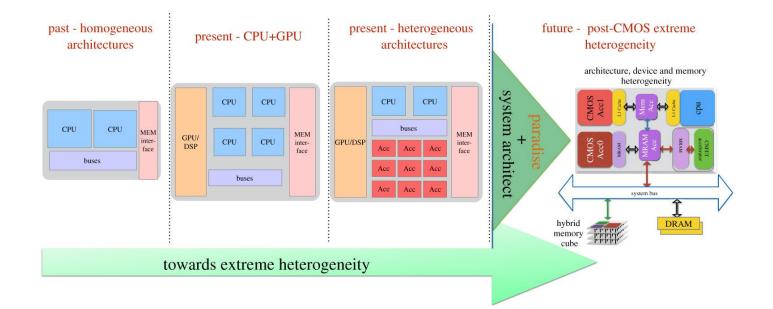

- Near-term response: architectural specialization and extreme heterogeneity

- Provide additional value to end application

https://doi.org/10.1098/rsta.2019.0061

### More than Moore and Beyond's Moore

Argonne National Laboratory is a U.S. Department of Energy laboratory managed by UChicago Argonne, LLC

### **Beyond's Moore- Challenges ahead**

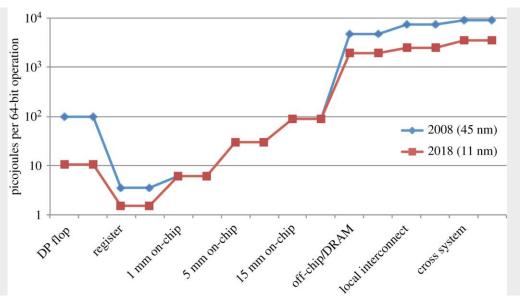

- Energy efficiency of transistors is improving as sizes shrink

- Energy efficiency of wires is not improving

We have come to a point where the energy needed to move data exceeds the energy used to perform the operation on those data

https://doi.org/10.1098/rsta.2019.0061

### HETEROGENEOUS INTEGRATION What's next?

- Advancing interconnect

- Advancing packaging, thermal interface etc

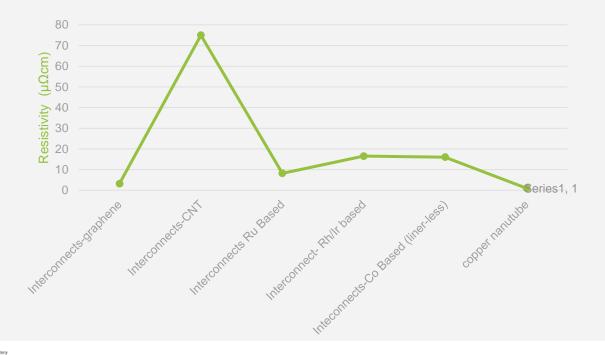

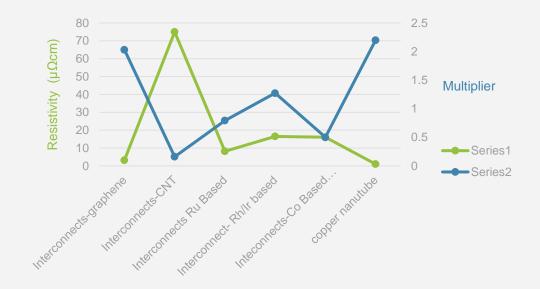

#### Advancing interconnect –replacing Cu

### Advancing interconnect –replacing Cu

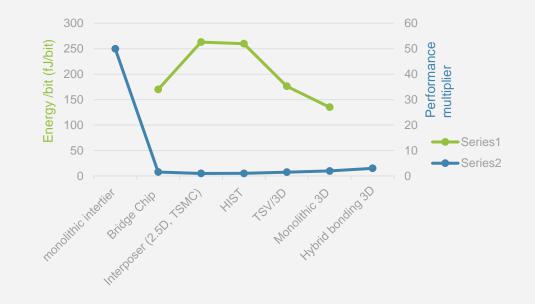

### Interconnects-for enabling chip stacking

#### Interconnects-for enabling chip stacking

# **THANK YOU**

CONTACT **Moinuddin Ahmed Technical Lead Electronic Materials Characterization Group** Phone: 630-252-5064 Email: mahmed@anl.gov